AMD EPYC PLATFORM

AMD EPYCプラットフォーム

AMDが「最高性能のx86 CPU」と謳うサーバーCPU 圧倒的な価格性能比・DDR5メモリ・PCIe Gen5 使いやすい高性能をお手元に。

EPYCシリーズは、2017年にAMD社がサーバ・組み込みシステム向けにリリースを開始したx86-64(x64)アーキテクチャのプロセッサです(コンシューマ向けはRyzenシリーズ)。高性能なメニーコアプロセッサで、コストパフォーマンスの点でも優れた製品です。HPC分野に加えて、仮想化環境/クラウド利用、メディア/エンタテインメント分野などでも注目されています。

BASIC CONFIGURATIONEPYCシリーズの基本構成

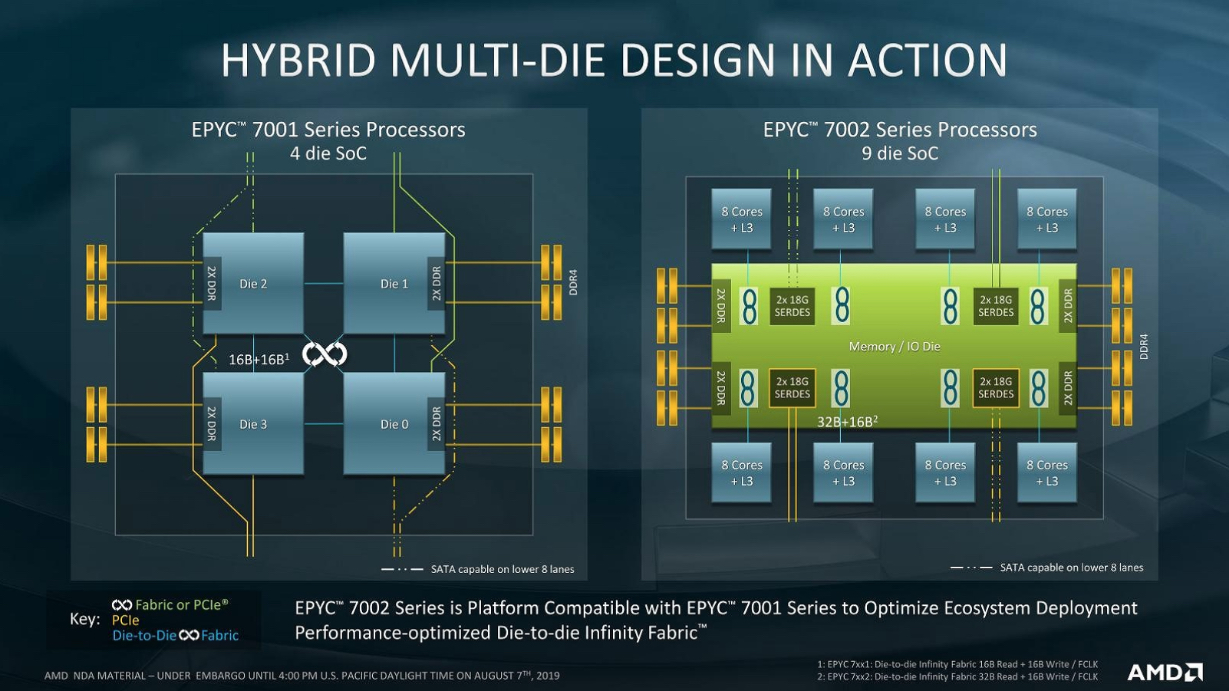

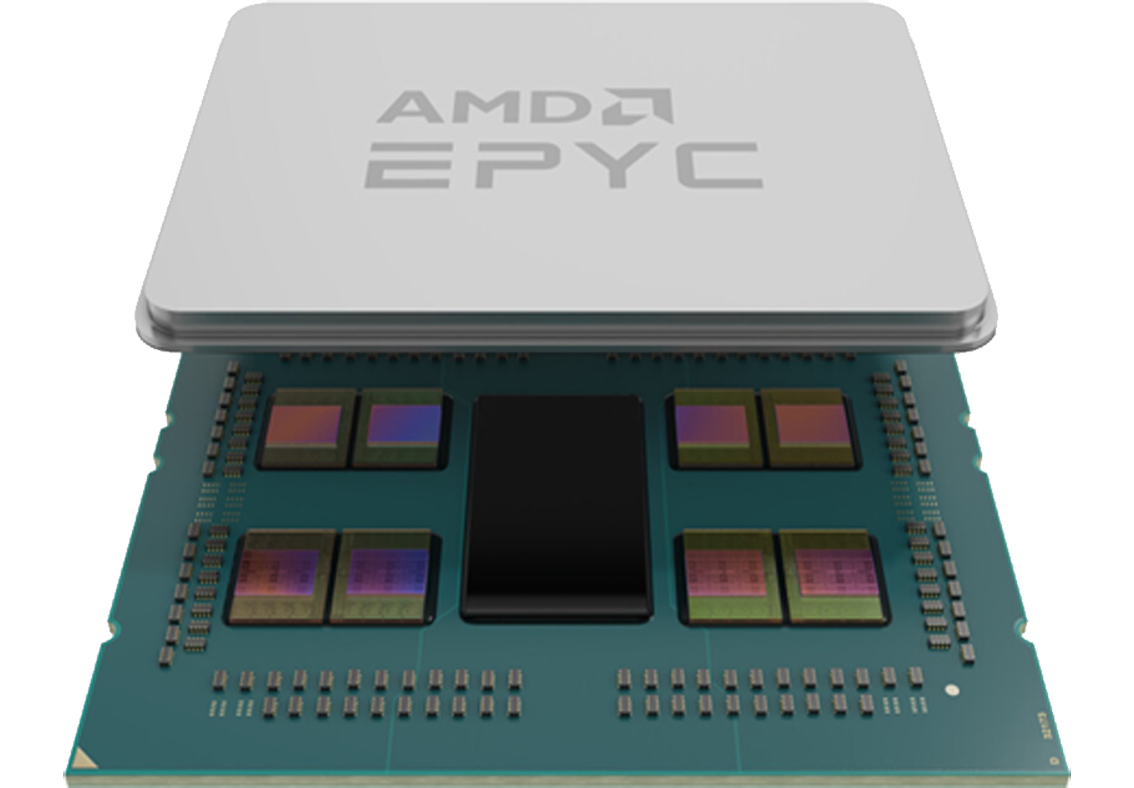

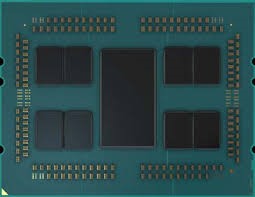

AMDは1つのCPUソケット上に多くのコアを集積する方法としてMCM(Multi-Chip Module)によるマルチダイ化を進めてきました。

EPYCプロセッサではダイはチップレットと呼ばれ、第2世代以後はCPUチップレット(CCD:CPU Complex Die)とI/Oチップレット(IOD:I/O Die)がそれぞれ独立して設計されています。

第2世代EPYC(Rome)、 第3世代(Milan)では、CCDの製造にTSMC 7nm/6nmプロセスを採用してダイを小型化。8コアのCCDを8モジュール搭載することに成功し、1CPUソケットあたり最大64コア/128スレッドの構成が可能になりました。

第4世代(Genoa)ではCCDに5nmプロセスを使用してチップレットをさらに小型化し最大コア数が96コアに増加。さらに新しいIODでDDR5メモリとPCIe 5.0に対応しました。

EPYC 9004シリーズ(開発コード名:Genoa/Genoa-X)

・Zen3アーキテクチャを改良したZen4アーキテクチャを採用しています。

・EPYC 9004シリーズではCCDが従来の7/6nmに代わって5nmのプロセスルールで製造され、より多くのCCDを搭載可能となりました。

・1CPUソケットあたり96コア/192スレッドまでのモデルがラインアップされています。

・IODが12チャネルの次世代メモリ規格DDR5に対応してさらに広帯域でのメモリアクセスが可能になったほか、PCI Express Gen5やCXL(Compute Express Link)1.1+などの高速I/O技術への対応が図られています。

・第4世代EPYC(Genoa)搭載サーバは絶対的な性能とコストパフォーマンスにより、HPC分野はもとより各種エンタープライズ用途、レンダリング処理を中心としたメディア/エンタテインメント、仮想環境やクラウドなど、幅広い分野での採用が見込まれます。

・第3世代EPYC(Milan-X)と同様に、L3キャッシュを3次元積層した大容量キャッシュメモリ版のGenoa-Xも近日登場する見通しです。

EPYC 7003シリーズ(開発コード名:Milan/Milan-X)

・Zen2アーキテクチャを改良したZen3アーキテクチャを採用しています。

・プロセスルールは7nmのまま、キャッシュ階層や内部の分岐予測、実行ユニットなどの見直しなどによるIPCの改善約19%増などの性能の向上と、セキュリティ関連機能に手が加えられました。

・第2世代EPYCシリーズとのソケット互換性を持ち、4/6/8チャネルDDR4のメモリ構成に対応し、用途に応じたより柔軟なメモリ構成が可能になりました。

・6nmプロセスで製造され、L3キャッシュを3次元積層することで大容量のキャッシュメモリを搭載したMilan-Xプロセッサは、メモリ帯域が性能に影響するHPCアプリケーションなどで顕著な性能向上を実現しました。

EPYC 7002シリーズ(開発コード名:Rome)

・第2世代EPYCプロセッサはZenアーキテクチャを改良したZen2アーキテクチャを採用し、7nmのプロセスルールで製造されました。

・実行効率が改善されてIPCが競合製品(Intel Xeon scalable)と同等になりました。

・プロセスの微細化によりチップレットのサイズが縮小され、1ソケットあたり最大64コア/128スレッドの製品がラインアップされました。

・8チャネルのDDR4メモリチャネル、最大128レーンPCIe Gen4をサポートする、コストパフォーマンスに優れた画期的な高性能プロセッサに進化しました。

・マルチスレッド機能の脆弱性による情報窃取への対応など、セキュリティ関連機能も強化されました。

FEATUREZen2/3アーキテクチャ(Rome/Milan)の特徴

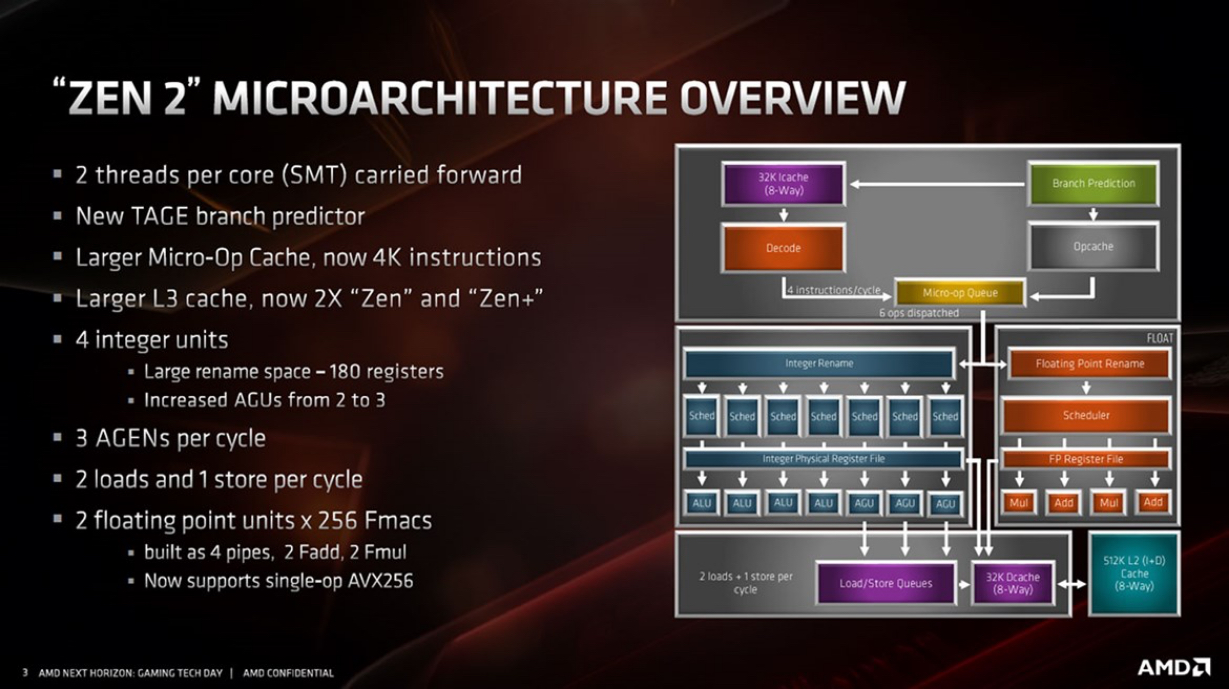

Zen2アークテクチャは、SIMD(Single Instruction Multiple Data)演算ユニットを128-bit幅から256-bit幅に拡張(浮動小数点演算性が2倍)し、1クロックで実行できる命令数(IPC:Instructions Per Cycle)を15%改善、動作クロックの向上、分岐予測の改良、キャッシュサイズの見直し、各種キューやレジスタの拡張など、Zenアークテクチャ(EPYC 7001シリーズ)から多岐にわたる改良が施されています。Zen3では更にIPCが19%改善されています。

Zen2/3プロセッサの基本構造は同じで、8コアを単位とした「Chiplet」チップ(CPU Complex ダイ)と、メモリコントローラやPCIeコントローラなど各種コントローラを集約したI/O Chiplet(sIOD:Server I/O ダイ)による構成となっています。そのためEPYC 7002シリーズ(開発コード名:Rome)及びEPYC 7003 シリーズ(開発コード名:Milan)は、最大8コア(1Chiplet)x8=64コアのプロセッサとなっています。

Rome/Milan搭載サーバーは絶対的な性能とコストパフォーマンスによって、HPC分野はもとより、消費電力効率の良さから各種エンタープライズ用途、レンダリング処理を中心としたメディア/エンタテインメント、仮想環境やクラウドでの利用など、広く活用されています。

↓ZenアーキテクチャとZen2/3アーキテクチャのデザイン比較

↓Zen2/3アーキテクチャの特徴

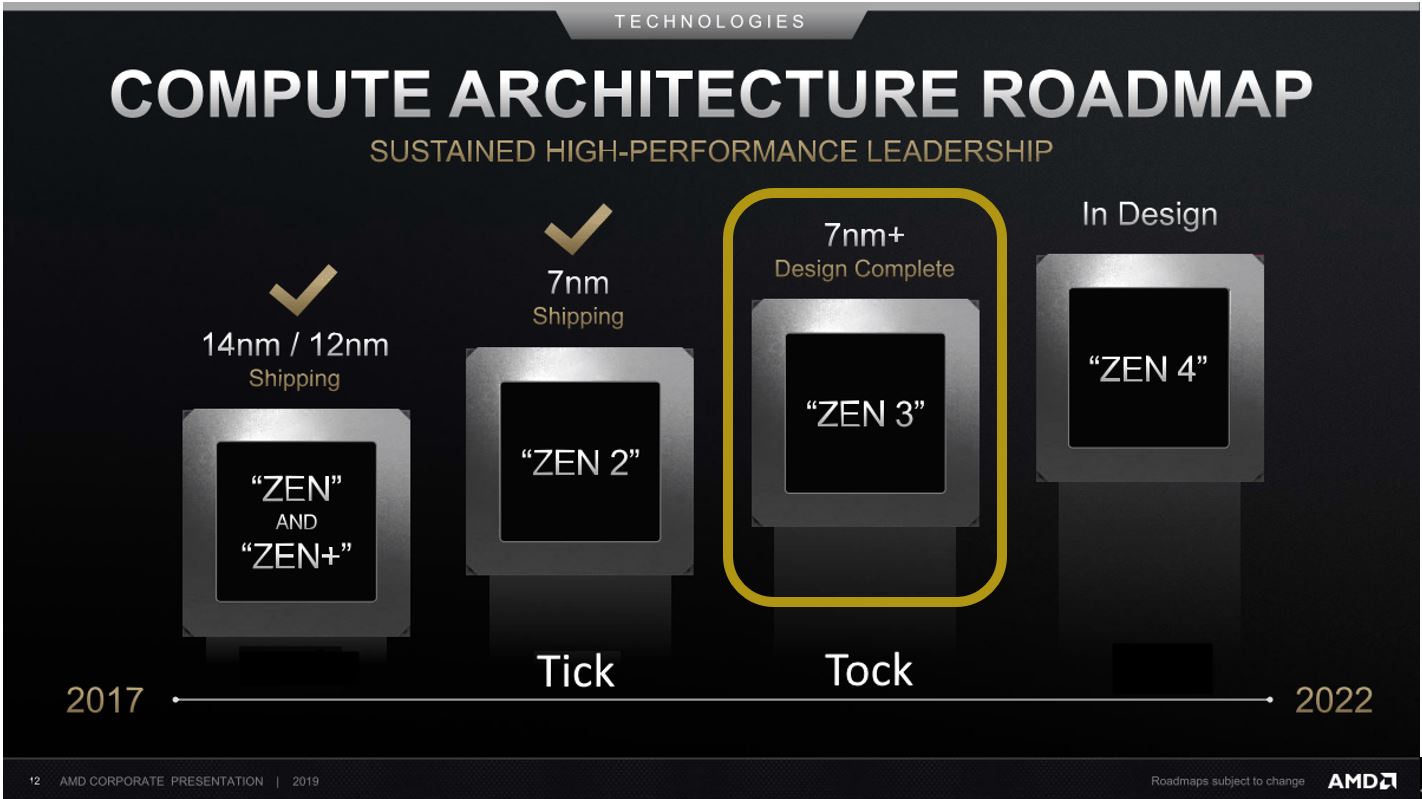

ROADMAP & OVERVIEWロードマップと機能の概要

※Tick – Tock(チク タック):新プロセス(微細化)の導入と、

CPUの基本設計(マイクロアーキテクチャ)の改良による性能向上を交互に行うCPUの開発モデル。

EPYC 9004シリーズ(Genoa)の概要

https://www.amd.com/ja/processors/epyc-9004-series

- “Zen4” CPU ・ 8 cores CCD × 12(96 cores / 192 threads) + IOD

- Socket SP5

- 320W-400W TDP

- 128 lanes PCIe 5.0, CXL 1.1+

- 12 channels DDR5-4800 memory

(up to 512GB/slot, Max 6TB)

・ CCD:5nm TSMC Process

Genoa/Genoa-X

EPYC 7003(Milan)、7003Xシリーズ(Milan-X)の概要

https://www.amd.com/ja/processors/epyc-7003-series

- “Zen3” CPU ・ 8 cores CCD × 8(64 cores / 128 threads) + IOD

- Socket SP3

- 155W-280W TDP

- 128 lanes PCIe 4.0

- 8/6 channels DDR4-3200 memory

(up to 256GB/slot, Max 4TB)

・ CCD:7nm(Milan)/6nm(Milan-X) TSMC Process

Milan/Milan-X

EPYC 7002シリーズ(Rome)の概要

https://www.amd.com/ja/processors/epyc-7002-series

- “Zen2” CPU ・ 8 cores CCD × 8(64 cores / 128 threads) + IOD

- Socket SP3

- 120W-225W TDP

- 128 lanes PCIe Gen4

- 8 channels DDR4-3200 memory

(up to 256GB/slot, Max 4TB)

・ CCD:7nm TSMC Process

Rome / Miran

SECURUTY FUNCTIONセキュリティ関連機能

EPYCプロセッサは、AMD独自のセキュリティ機能群「Infinity Guard Security」を実装しています。

https://www.amd.com/ja/technologies/infinity-guard

たとえば、SME:Secure Memory Encryption機能は、メモリ空間への直接攻撃や、物理的にサーバにアクアセスするコールドブートアタックに対応するため、暗号化されたメモリへのアクセスをサポートします。

また仮想環境向けに、SEV:Secure Encrypted Virtualization機能を実装し、暗号鍵を生成して仮想マシン(VM)同士を隔離することで、1つの仮想環境の管理者権限やハイパーバイザが攻撃者に侵害された場合でも、その他の仮想マシンを保護することができます。

Zen2:EPYC7002シリーズ(Rome)以降のEPYCプロセッサでは、CPUとは独立したASP:AMD Secure Processerを内蔵しており、「Root of Trust」としてブートROM/ブートローダ/BIOSといった各層での認証を行いOSのセキュアなBootを保証します。これによりBIOS改ざん攻撃などに対するハードウェアレベルのセキュリティ機能を提供しています。またSEVの暗号鍵の生成などもASPが行います。

Zen3:EPYC7003シリーズ(Miran)では、仮想環境向けのセキュリティであるSEVが、従来のVM単体からVMの中に作られたVM(ネストされたVM)にも適用される(SEV-ES)など、強化されています。

- SEV:Secure Encrypted Virtualization

Encrypt Each VM with Unique Keys - SEV-ES:SEV – Encrypted State

VM Integrity with Protected CPU Registers - SEV-SNP:SEV – Secure Nested Panging

Hardware Protection Against Malicious Hypervisors

※Root of Trust:デバイスの信頼性を保証するための、ハードウェア/ソフトウェアコンポーネント。ソフトウェアの完全性検証とは、セキュアブート及び、セキュアアップデート機構をいう。